# POWER REDUCTION IN DOMINO LOGIC **USING CLOCK GATING IN 16NM CMOS TECHNOLOGY**

Mr.R.Nagaraju, M.Tech. Electronics and Communication Engineering Annamacharya Institute of Technology &Sciences Tirupati,India rnagarajuece@gmail.com

P.Bhaskar Ramesh sai Electronics and Communication Engineering Annamacharya Institute of Technology &Sciences Tirupati,India palisettibhaskarrameshsai@gmail.com

N.Bharath Chand Electronics and Communication Engineering Annamacharya Institute of Technology &Sciences Tirupati, India bharathchand1234@gmail.com.

N.Bharath Electronics and Communication Engineering Annamacharya Institute of Technology &Sciences Tirupati, India narabharath9182@gmail.com

Y.Jayasurya **Electronics and Communication** Engineering Annamacharya Institute of Technology &Sciences Tirupati,India suryayeduru333@gmail.com

#### **Abstract**

Power consumption is a serious issue in today's VLSI circuit design, especially in deep-submicron technologies. CMOS NAND logic and domino logic are two popular design styles, each with different power consumption behaviors. Historically, domino logic has been regarded as powerconsuming as a result of constant clock switching. Still, our simulation output for a 16nm CMOS process demonstrates that domino logic is power-consuming (2.05  $\mu$ W) versus CMOS NAND logic (3.8 µW). It saves 46.05% power when implementing domino logic rather than dynamic CMOS NAND logic and domino logic versus dynamic CMOS Nand logic static power saving is 99.99%.

In order to compare more thoroughly the influence of the style of logic on power, we compare the 1-bit and 4-bit full adders. From the results, it is apparent that the domino logic's power benefit does not vary for circuits of various complexities. Power reduction is realized by having fewer transistors, less switching capacitance, and an enhanced charge-sharing technique in domino logic. These results indicate that domino logic can be used as a power-efficient alternative for highspeed, low-power digital circuit designs in advanced CMOS technology nodes.

Keywords- Staic, Dynamic, CMOS, Domino logic, Clock gating.

#### 1.INTRODUCTION

As CMOS technology is reduced to ultra-deep-submicron and deep-submicron nodes, power consumption has emerged as a key issue in VLSI circuit design. As supply voltage, device size, and threshold voltages continue to decrease in a persistent manner, leakage currents have risen, contributing significantly to static power dissipation. Dynamic power used to be predominant over static power in larger technology nodes (>350nm), but in sub-100nm.technologies, static power dissipation has emerged as a serious issue.

Domino logic has received considerable interest in VLSI design because of its high-speed operation and less space than in static CMOS. In contrast to static CMOS logic, which uses complementary transistors for every logic function, domino logic employs a precharge-evaluate technique and is therefore faster and more efficient for high-performance designs. Nevertheless, the domino logic's continuous clock switching results in higher power dissipation, especially in standby mode. Several methods have been suggested to counter this problem, including low-swing clocking, supply voltage scaling, and clock gating.

This work targets power comparison between static and dynamic power of domino logic and CMOS NAND logic in a 16nm CMOS process, targeting 1-bit and 4-bit traditional full adders. Our simulation results prove that domino logic uses less power (2.05 μW) than CMOS NAND logic (3.8 μW), realizing a 46.05% reduction in dynamic power as same as 4-Bit conventional full adder uses less power compared to 1-Bit realizing a 60% reduction in dynamic power. The findings contradict traditional assumptions regarding domino logic as power-hungry and demonstrate its potential as a low-power alternative in contemporary VLSI design. Additional examination of full adder circuits validates the consistent power savings of domino logic over CMOS NAND logic.

# 2. EXISTING METHOD

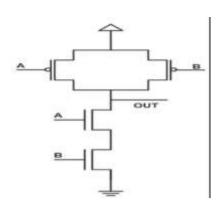

#### 1. CMOS NAND Logic

A CMOS NAND gate is constructed out of PMOS and NMOS transistors. The number of the transistors utilized follows this general rule: for a NAND gate is made out of The pull-up network and two series NMOS transistors is made out of two parallel PMOS transistors.

Structure and Operation:

Fig.1. Basic CMOS NAND Circuit

#### Pull-Up Network (PUN):

- Constructed by connecting parallel PMOS transistors.

- •Ensures the output to be HIGH (1) unless all inputs are HIGH.

#### The Pull-Down Network (PDN):

- •PDN is constructed by connecting NMOS transistors in

- •Guarantees that only when all of the inputs is high will LOW (0) is the output.

#### Truth Table:

| A | В | OUTPUT(Y) |

|---|---|-----------|

| 0 | 0 | 1         |

| 0 | 1 | 1         |

| 1 | 0 | 1         |

| 1 | 1 | 0         |

Fig. 2. NAND Truth table

## Power Dissipation issues:

- Ongoing switching of the clock results in dynamic power consumption at high levels.

- A pulse-shaped output ensures higher power usage in standby.

#### 1-Bit Traditional full adder

- A 1-bit full adder is an elementary arithmetic building block that calculates the sum of three binary input: A,B and Carryin(Cin).

- Boolean Equations:

- Sum (s) =  $A \oplus B \oplus Cin$

- •Carry out (Cout)= AB + BCin + ACin

- The traditional 1-bit full adder is implemented using dynamic logic gates, which are:

- AND gates for generating carry. XOR gates for generated sums. OR gate for output in final carries

# March 2025 IJSDR | Volume 10 Issue 3

· Takes advantage of clock gating to enhance power efficiency.CMOS NAND Logic and Full Adder 1-bit in domino logic are power-hungry due to constant clocking.

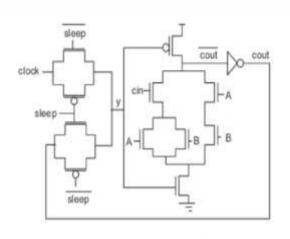

Fig. 3. A 1-bit conventional full adder circuit

#### 3. PROPOSED METHODOLOGY

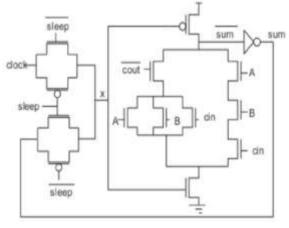

2 Input nand gate using Domino logic

Domino logic is a changeable logic family used in high-speed VLSI circuits. It operates in 2 phases:

1. Phase of Precharge (Clock = 0)

The dynamic A PMOS transistor charges node (X) to VDD. The output remains low until evaluation.

2. Phase of Evaluation (Clock = 1)

If the pull-down network (PDN) does conduct (i.e., inputs permit discharge), X, the dynamic node, discharges to zero, generating an output of 1.If the PDN doesn't conduct, the dynamic node maintains its precharge value (1), and the output remains low Standard Limitations of Domino Logic

Fig. 4. 2 Input nand gate using domino logic

March 2025 IJSDR | Volume 10 Issue 3 Advantages of Output Hold:

#### 4-Bit Conventional Full Adder

A full adder 4-bit is an analog digital circuit used in 4-bit two numerical addition. It consists of four cascaded 1-bit full adders, where the carry output of one stage is fed as the carry input to the next stage. The primary function of this circuit is to add Provide a 4-bit sum and carry using two 4-bit binary numbers and a carry input. Each 1-bit full adder contains 2x1 multiplexer to reduce the power.

Fig . 5. 4-Bit Full Adder Block diagram

#### 4. THE PROPOSED METHODOLOGY IMPROVES POWER EFFICIENCY BY INTRODUCING

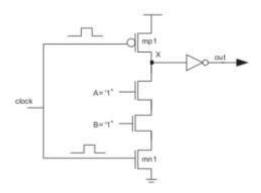

Clock Gating: Prevents the clock to switch when inputs don't

In Domino Logic, circuits go through two different phases:

a. Precharge Phase: Clock State: when the clock reads zero. The node that is dynamic (X) is precharged to (logic high, '1') by a PMOS transistor. The NMOS pull-down network (PDN) is OFF, so it does not discharge. The output is stable.

Purpose: Causes the node to be precharged prior to entering the evaluation phase.

Example in a 4-bit Full Adder (Domino Logic): Every component of the adder has a precharge circuit. When, all dynamic nodes (X0, X1, X2, X3) are precharged to logic high (1). Carry propagation circuits are also precharged.

b. Evaluation Phase: Clock State: Once the clock () is high (1). Operation The Nmos transistor and the Pmos transistor are both off. pull-down network (PDN) is ON.

In the event that the inputs are such that the PDN carries, the node discharges to 0.Otherwise, the node keeps its precharge value.

Purpose: Computes the final output of the circuit.

Example in a 4-bit Full Adder (Domino Logic): When sum bits are required to be '1', the dynamic node stays charged. When sum bits are required to be '0', the dynamic node is discharged via the NMOS network.

Output Hold Circuit: Maintains the previously computed output, precluding unnecessary transitions. Output hold is a term used to describe a circuit's capability to hold its output value even when the inputs no longer change. Output hold is crucial in a 4-bit adder in applications where the adder must have its sum and carry outputs maintained while precluding unnecessary transitions that consume power.

# Prevents Unnecessary Power Consumption: Prevents continuous enabling and disabling of outputs.

- Improves Stability: Provides stable output even if the inputs are no longer changing.

- Decreases Switching Activity: Essential in low-power VLSI designs such as Domino Logic adders.

## 3. Multiplexer (MUX)-Based Clock Control:

Utilizes a 2:1 MUX to switch from the clock signal to the output. A 2:1 multiplexer is employed to switch between the newly computed output and the old value stored.

#### 5. IMPEMENTATION&SIMULATON

Fig. 6. Output of CMOS NAND Logic

Power Dissipation in Simple CMOS NAND Logic: The specified power dissipation is 3.8 µW. Dynamic power is predominantly responsible for the total power consumption, largely because of repeated switching actions.

Fig. 7. Power utilization of Basic CMOS NAND Logic.

#### ISSN:2455-2631

Fig. 8. Output of 2-bit NAND Using Domino Logic.

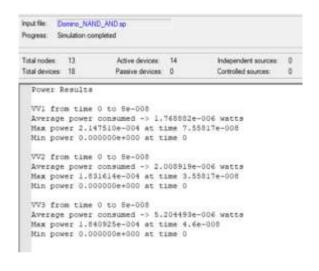

Power Dissipation in Domino Logic: The power dissipated is 2.05 µW, less than simple CMOS NAND logic. This is mainly because of efficient circuit design and clock gating methods.Dynamic power reduced results in less overall power dissipation, thus the circuit becomes more energy- efficient.

Fig.9. Power Utilization of 2-Bit NAND Using Domino Logic.

Fig. 10. Output of 1-Bit conventional Full Adder

Power Consumption in 1-Bit Full Adder: The total power consumed is 15 µW. This increase is due to the complexity of the circuit, involving multiple logic gates.

# March 2025 IJSDR | Volume 10 Issue 3

Fig.11. Power utilization of Full Adder 1-Bit conventional.

Fig. 12. Output of 4-Bit conventional Full Adder

- Power Consumption in 4-bit full adder: The total power consumed is 24 µW.This methodology improves the power efficiency by introducing

- Clock gating

- Output hold circuit

- Mux based clock control

# 6.COMPARISON

#### TABLE I

| Logic Type      | Power       | Percentage of |

|-----------------|-------------|---------------|

|                 | Consumption | Original      |

|                 | (µW)        | power(%)      |

| CMOS NAND       | 3.8         | 100           |

| Logic           |             |               |

| Proposed Domino | 2.01        | 52.9          |

| Logic           |             |               |

| Power Reduction | 1.79        | 47.1          |

|                 |             |               |

This Table .I shows that proposed Domino Logic reduces power consumption by 1.79uW, which is a 47.1% reduction compared to the CMOS NAND Logic.

#### TABLE II

| Full Adder Type   | Power       | Percentage of  |

|-------------------|-------------|----------------|

|                   | Consumption | Expected Power |

|                   | $(\mu W)$   | (%)            |

| 1-bit             | 15          | 100            |

| Conventional Full |             |                |

| Adder             |             |                |

| Expected 4-bit    | 60          | 100            |

| Conventional FA   |             |                |

| Proposed 4-bit    | 24          | 40             |

| Conventional FA   |             |                |

| Power REduction   | 36          | 60             |

|                   |             |                |

This Table II. shows that proposed 4-bit full adder reduces power consumption by 36  $\mu$ W(60%).

#### 7. Conclusion

In conclusion, CMOS domino logic provides high-speed operation with reduced area compared to static CMOS logic. However, its continuous clock switching leads to significant power dissipation. Clock gating in domino logic, especially in circuits like 1-bit and 4bit conventional full adders, effectively reduces static and dynamic power consumption by bypassing the clock during standby mode while retaining circuit state. The proposed technique achieves substantial power savings, making it suitable for low-power applications in ultra-deep submicron technology.

#### 8. References

- [1].G. K. Yeap (2012) This book provides practical strategies for designing low-power digital VLSI circuits, addressing power optimization techniques at various design levels. It covers transistorlevel optimizations, circuit techniques, and system-level methodologies.

- [2].S.-Y. Ahn and K. Cho (2014) Proposes a smalldomino logic circuit using twist-connected transistors to reduce power consumption and improve performance. The approach minimizes voltage swings, reducing dynamic power dissipation and enhancing speed.

- [3].J. Pretorius et al. (1985) Analyzes domino CMOS logic circuits and their optimization for standard cell design. It provides insights into power, delay, and noise considerations, offering guidelines for improving efficiency in digital implementation.

- [4].S.-O. Jung et al. (2002) Introduces a low-swing clock domino logic technique that incorporates dual supply and dual threshold voltages. This method effectively reduces power consumption while maintaining performance in high-speed digital circuits.

- [5].M. R. Casu et al. (2002) Presents a reduced clock swing domino gate implemented in Silicon-On-Insulator (SOI) technology. The technique aims to lower dynamic power consumption while preserving the speed benefits of domino logic.

- [6].S. Farah and M. Bayoumi (2013) Proposes a comprehensive operand-aware dynamic clock gating technique for low-power domino logic. The method optimizes power consumption by selectively gating the clock signal based on operand activity, reducing unnecessary switching.

- [7].J. M. Rabaey et al. (2002) A fundamental textbook on digital integrated circuits covering design principles, low-power techniques, and high-performance circuit implementations. It serves as a key reference for students and professionals in VLSI design.

- [8].S.-O. Jung et al. (2001) Develops Skew-Tolerant High-Speed (STHS) domino logic, which enhances timing robustness against clock skew and improves operational speed. The approach makes

# domino logic circuits more reliable in high-frequency applications.

- [9].S. Garg and T. K. Gupta (2018) Discusses low-power domino logic circuits in deep-submicron technology using CMOS, focusing on techniques to reduce power consumption and improve performance.

- [10].A. Anita Angeline and V. S. Kanchana Bhaaskaran (2022) -Provides a review of domino logic keeper circuit design techniques, analyzing various approaches to enhance noise immunity and reduce power dissipation.

- [11].C.-Y. Wu et al. (1993) Analyzes and designs a new race-free four-phase CMOS logic, addressing issues related to timing and power consumption in domino logic circuits.

- [12].R. H. Krambeck et al. (1982) Introduces high-speed compact circuits with CMOS, laying the foundation for domino logic design and its applications in low-power circuits.

- [13].S. Farah and M. Bayoumi (2013) Propose a comprehensive operand-aware dynamic clock gating scheme for low-power domino logic, aiming to reduce power consumption by selectively gating the clock based on operand activity.

- [14].M. R. Casu et al. (2002) Present a reduced clock swing domino gate in SOI technology, focusing on lowering power consumption while maintaining performance.

- [15].S.-O. Jung et al. (2002) Introduce a low-swing clock domino logic technique incorporating dual supply and dual threshold voltages to achieve low power consumption in high-speed circuits.

- [16].J. Pretorius et al. (1985) Analyze and design optimization of domino CMOS logic with application to standard cells, providing insights into power, delay, and noise considerations.