# IMPLEMENTATION OF DIGITAL MODULATION SCHEMES USING VERILOG HDL

# Rashmi A

#### Student

East point college of engineering

*Abstract*-This paper describes the design and development of an FPGA-based digital Modulation Scheme for highresolution Communication Application. We are focusing on implementation of Verilog based code simulation for fundamental and widely used digital modulation techniques such as Binary Amplitude-shift keying (BASK), Binary Frequency-shift keying (BFSK), Binary Phase-shift keying (BPSK) and Quadrature Phase Shift Keying(QPSK). In this work the idea of sinusoidal signals that have been generated is plain sailing in nature and based on fundamentals of signal sampling and quantization. Such concept of sinusoidal signals generation is not unfamiliar but somehow simplified using sampling and quantization in time and amplitude domain, respectively. The whole simulation is done on Modelsim and Xilinx-ISE using VERILOG Hardware descriptive language. The work has been accomplished on Thirty two bit serial data transmission with self-adjustable carrier frequency and bit duration length.

# I. INTRODUCTION

Modulation is the process of varying one or more properties of a periodic waveform, called the carrier signal, with a modulating signal that typically contains information to be transmitted. Most radio systems in the 20th century used frequency modulation (FM) or amplitude modulation (AM) to make the carrier carry the radio broadcast. In general telecommunications, modulation is a process of conveying message signal, for example, a digital bit stream or an analog audio signal, inside another signal that can be physically transmitted. Based on what parameter is changed the different types of modulation techniques are Binary shift keying (BASK). Binary frequency shift keying (BFSK), Binary phase shift keying(BPSK) and Quadrature phase shift keying(QPSK).

The ASK modulation/demodulation scheme, for both RF-band and baseband transceiver, was presented. This design is realized on future mobile memory I/O interface for energy efficient. However, BPSK is as well as showing better Bit. These digital modulation techniques were implemented on FPGA device. Simulation results consist of bit error rate of digital signals of modulators, source consumption of BASK, BFSK, BPSK and QAM FPGA-based, bit rate of BASK and BPSK on Xilinx ISE suite complier using verilog language. Thus digital modulators were implemented on FPGA. In addition to, bit error rate of BASK and BPSK modulation techniques was compared using Xilinx. In this paper, for BPSK and BASK modulation, FPGA based modulator is presented. Finally, simulation results are obtained.

# II. **OBJECTIVE:**

The objective of this paper is to implement fully DDS based digital BASK, BFSK, BPSK & QPSK modulators that employ the minimum number of digital blocks suitable for software-defined radio systems and are implemented individually into the Spartan 3 FPGAs. The input carrier signal and message signal is generated using DDS, for more scalability or flexibility. Furthermore, the implemented FPGA designs can be used in a digital communication system to Demonstrate BASK, BFSK, QPSK and BPSK digital modulation techniques. Digital modulation and demodulation can be implemented on FPGA and received considerable attention. Here modulation is done without multiplication of binary massage signal with sinusoidal carrier signal. Instead of multiplication, for each case, sample of different carrier signal was saved in ROM.

# III PROPOSED SYSTEM:

The proposed method produces the BASK/BFSK signal which is based on stored BASK/BFSK phase data in ROM. This method eliminates completely the DDS and multiplier blocks of the modulator. The modulator design has been made generic so that it can be used as either BASK or BFSK by use of single operational switch.

#### **GENERAL:**

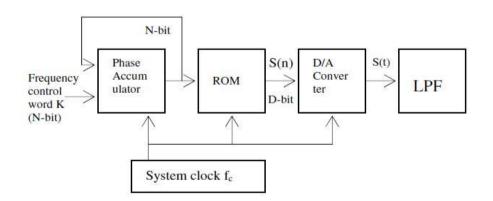

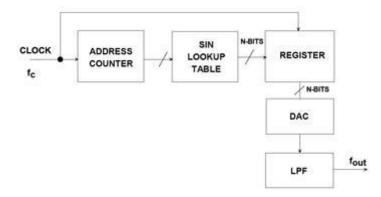

#### Fig. 1 Block diagram for storing phase data

#### **PROPOSED SYSTEM BLOCK DIAGRAM:**

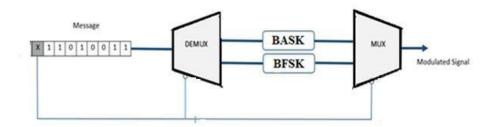

#### Fig. 2 Proposed block diagram

Here one 1:2 multiplexer and one 2:1demultiplexer is used .Here,there will be three modulation techniques, namely ASK & FSK. There will be 10 bits of message signal where first two bits comprises of selection line and rest of 8 bits will be treated as message signal.

Since selection line is of one bits, so there will be two combinations  $(2^1=2)$  in generel. Combinations are 0,1. Here this combination will be ignored because only two types of combinations of needed for two modulation techniques. The select line combination 0 will active the BASK module, 1 will active for BFSK module.

Now the above mentioned 1 bits will enter into the demultiplexer.0,1 bits will enter serially in the demultiplexer. Actually in this case serial communication system is used for data transmission. Now the modulation technique will be selected as per the select line bit will enter into the demultiplexer through meassage bits. Now for example if 0 select line is entered through the message bit in the demultiplexer, then BPSK module path will get activated, that means BASK modulation technique will be selected. Now the same thing will be repeated in the case of select line 1 here BFSK module path will be selected respectively as the modulation technique. Actually demux select the path of module. So, from demux rest of message bits are tranmitted towards the path.

Now whichever modulation technique will be selected from the above process for example either BASK, BFSK their modulated ouput bits will enter into the multiplexer. Here single output multiplexer is used. Now as the output we got the message bits which we had given as the input (8 bit). The final output will be in the form of modulated sinusoidal waveform according to the modulation scheme used.

#### **PROPOSED SYSTEM TECHNIQUE:**

Digital Modulation BASK and BFSK

#### **PROPOSED SYSTEM ADVANTAGES:**

- Low Complexity

- Low Power

- Feasible to use for different performance

#### **MODULES SEPERATION:**

- BASK Modulation

- BFSK Modulation

- DDS Design

- Counter

- Registers

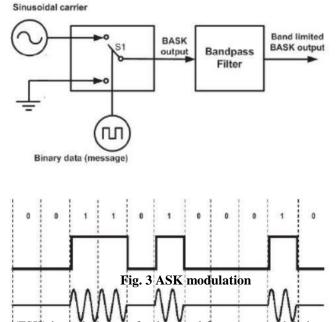

**BASK MODULATION:** In BASK, the amplitude of the sinusoidal carrier signal is changed according to the message level ("0" or "1"), while keeping the phase and frequency constant. The following figure represents the block diagram of BASK.

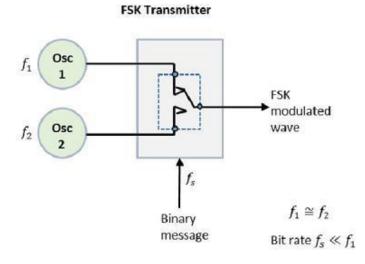

#### **BFSK:**

Frequency-shift keying (FSK) is analogous to fundamental frequency modulation technique in which digital information is transmitted through deviating the frequency of the carrier signal. The carrier frequency is shifted in according to the input data stream; phase and amplitude of the carrier are maintained constant.

The FSK modulator block diagram comprises of two oscillators with a clock and the input binary sequence. Following is its block diagram.

#### Fig. 4 BFSK

The two oscillators, producing a higher and a lower frequency signals, are connected to a switch along with an internal clock. To avoid the abrupt phase discontinuities of the output waveform during the transmission of the message, a clock is applied to both the oscillators, internally. The binary input sequence is applied to the transmitter so as to choose the frequencies according to the binary input.

#### DDS:

Direct digital synthesizer (DDS) is a type of frequency synthesizer used for creating arbitrary waveforms from a single, fixedfrequency reference clock. Applications of DDS include: signal generation, local oscillators in communication systems, function generators, mixers, modulators, sound synthesizers and as part of a digital phase-locked loop.

A basic Direct Digital Synthesizer consists of a frequency reference (often a crystal or SAW oscillator), a numerically controlled oscillator (NCO) and a digital-to-analog converter (DAC) as shown in Figure 1. The reference oscillator provides a stable time base for the system and determines the frequency accuracy of the DDS. It provides the clock to the NCO which produces at its output a discrete-time, quantized version of the desired output waveform (often a sinusoid) whose period is controlled by the digital word contained in the Frequency Control Register. The sampled, digital waveform is converted to an

analog waveform by the DAC. The output reconstruction filter rejects the spectral replicas produced by the zero-order hold inherent in the analog conversion process.

Figure 5 Direct Digital Synthesizer block diagram

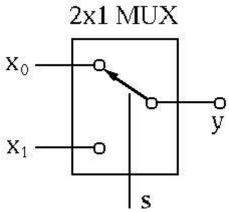

#### **MULTIPLEXERS:**

A multiplexer (or mux) is a device that selects one of several analog or digital input signals and forwards the selected input into a single line. A multiplexer of  $2^n$  inputs has [n] select lines, which are used to select which input line to send to the output.

#### **M-BIT INPUT REGISTER:**

M-Bit Register Register Consist of M-Flip Flops. Flip-flop is a 1 bit memory cell which can be used for storing the digital data. To increase the storage capacity in terms of number of bits, we have to use a group of flip-flop. Such a group of flip-flop is known as a Register. The n-bit register will consist of n number of flip-flop and it is capable of storing an n-bit word.

# **PROPOSED SYSTEM ADVANTAGES:**

- Low Complexity

- Low Power

- Feasible to use for different performance

# IV SIMULATION AND SYNTHESIS RESULTS ANALYSIS

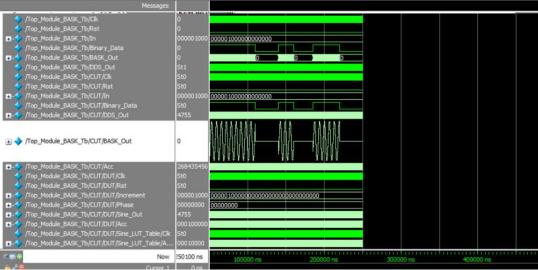

In order to verify the design, the entire system is simulated in the modelsim environment and synthesized in the Xilinx environment. The results are shown below for different modulation techniques.

The Fig. Shows the BASK method wherein the signal contains sine wave for a 1 binary signal and 0 for 0 binary signal and the status of different components and signals during this condition.

Fig. 6 Simulation result for BASK condition

The Fig. Shows the BFSK method wherein the signal contains two different signal frequencies based on input condition and the status of different components and signals during this condition.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Messages                                                                                 |                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------|

| // Top_Module_BFSK_Tb/Clk // Top_Module_BFSK_Tb/Rt // Top_Module_BFSK_Tb/In1 // Top_Module_BFSK_Tb/In1 // Top_Module_BFSK_Tb/Innary_Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0<br>0<br>00000 1000000000<br>00000 10 10 11 11 1<br>0                                   |                                       |

| ★ /Top_Module_BFSK_Tb/BFSK_Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4755                                                                                     |                                       |

| / Top_IMode_BFST_IbU/I/Ok / Top_IMode_BFST_IbU/I/Ok / Top_IMode_BFST_IbU/I/Ok / Top_IMode_BFST_IbU/I/Oh // To | 5t0<br>5t0<br>00000100000000<br>00000101011111<br>5t0<br>4755<br>-14810<br>268435456     |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -1282473984<br>St0<br>St0<br>00000100000000<br>00000000<br>4755<br>00010000000000<br>St0 |                                       |

| Among Module_BFSK_Tbj(CUT)/DUT1/Sme_LUT_Table/Address Among Module_BFSK_Tbj(CUT)/DUT1/Sme_LUT_Table/Sine Among Module_BFSK_Tbj(CUT)/DUT2/Cik                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00010000<br>4755<br>5t0<br>Now 250100 m<br>Cursor 1 0 m                                  | 40000 Hs 80000 Hs 120000 Hs 160000 Hs |

Fig. 7 Simulation result for BFSK condition

The device utilization summary indicates the number of flip flops used along with I/Os and BUFMUX utilized in the design. This is shown in below fig.

| Logic Utilization                              | Used | Utilization |

|------------------------------------------------|------|-------------|

| Number of Slice Flip Flops                     | 16   | 1%          |

| Number of 4 input LUTs                         | 32   | 1%          |

| Logic Distribution                             |      |             |

| Number of occupied Slices                      | 16   | 1%          |

| Number of Slices containing only related logic | 16   | 107%        |

|                                                | 0    | 0%          |

| Total Number of 4 input LUTs                   | 32   |             |

| Number used as logic                           | 10   |             |

Fig. 8 Device utilization summary

# CONCLUSION:

The work can be concluding that the implemented four types of modulators in the Simulation environment like BASK, BFSK using system generator on FPGA. The will be like to extend my current work by implementing all modulation techniques thus whole digital laboratory can be done on a single kit. FPGA implementations of BASK, BFSK digital modulators could be demonstrated. The main advantage of the implementations is the minimum numbers of digital blocks used for performing digital modulations, the ability to integrate with modules in FPGA boards, and the user controllability of the input signal's frequencies. The implemented FPGA designs are suitable for realization of the digital baseband-modulation part of software-defined radio systems. In addition, usage of this kind of implementation for educational purposes in digital communications laboratories or courses clearly emphasizes the correlation between different courses in electronics engineering. BASK, BFSK system (modulation) is designed using Verilog HDL and implemented on Spartan-3 FPGA kit.

#### **REFERENCES:**

- 1. J. G. Proakis, Intersymbol interference in digital communication systems. Wiley Online Library, 2003.

- 2. E. A. Lee and D. G. Messerschmitt, Digital communication. Springer Science & Business Media, 2012.

- 3. S. S. Haykin, M. Moher, and T. Song, An Introduction to Analog and Digital Communications. Wiley New York, 1989, vol.1

- 4. B. P. Lathi, Modern Digital and Analog Communication Systems 3e Osece. Oxford university press, 1998.

- 5. A. B. Carlson and P. B. Crilly, "Communication systems, 5e," 2010.

- 6. S. M. Alamouti, "A simple transmit diversity technique for wireless communications," IEEE Journal on selected areas in communications, vol. 16, no. 8, pp. 1451–1458, 1998.

- 7. A. Goldsmith, Wireless communications. Cambridge university press, 2005.

- 8. M. Mano, "Digital logic," Computer. Design, PrenticeHall, Inc. New Jersey, IX, vol. 7, 1999.

- 9. F. Quadri and A. D. Tete, "Fpga implementation of digital modulation techniques," in Communications and Signal Processing (ICCSP), 2013 International Conference on. IEEE, 2013, pp. 913–917.

- 10.B. Razavi and , Design of analog CMOS integrated circuits. , 2001. [11] S. Palnitkar, Verilog HDL: a guide to digital design and synthesis. Prentice Hall Professional, 2003, vol. 1.

- 11. V. Anitha and R. Kanchana, "VLSI Implementation of Oqpsk for Biomedical Devices Applications," International Journal of Technology and Engineering System (IJTES), Jan- March 2011, Vol 2, .No1.

- 12. Simon Haykin, "Communication Systems," Fourth Edition, PSN, 2008.

- 13.S.O. POPESCU, A.S. GONTEAN, "Performance comparison of the BPSK and QPSK Modulation Techniques on FPGA", IEEE 17th International Symposium for Design and Technology in Electronic Packaging (SIITME), 2011.

- 14.C. Erdoğan, I. Myderrizi, and S. Minaei, "FPGA Implementation of BASK-BFSK-BPSK Digital Modulators," IEEE Antennas and Propagation Magazine, Vol. 54, No. 2, April 2012.

- 15. Manoj Barnela, "Digital Modulation Schemes Employed in Wireless Communication: A Literature review," International Journal of Wired and Wireless Communications, Vol.2, Issue 2, April, 2014.

- 16. Ravisha, Saroj, "BER Performance for M-ARY Digital Communication", International Journal of Science and Research (IJSR), Volume 3 Issue 5, May 2014

- 17.K. Anitha, Umesharaddy, B. K. Sujatha, "FPGA Implementation of High Throughput Digital QPSK Modulator using Verilog HDL," International Journal of Advanced Computer Research, Volume-4, Number-,1 Issue-14 March-2014.

- 18.K. Mounica, S. Mohan Das, P. Uday Kumar, "A Verilog Design in FPGA Implementation of Quadrature Phase Shift Keying (QPSK) Digital Modulator," International Journal of Engineering Sciences & Research Technology, ISSN: 2277-9655, July 2013

- 19. Thotamsetty M Prasad, and Syed Jahingir, "Simulation and implementation of a BPSK modulator on FPGA," International Conference on Electronics and Communication Engineering (ICECE), 16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

- 20. User guide for Xilinx ISE, http://www.xilinx.com/support/documentation.

- 21.FPGA: http://www.xilinx.com/products/fpga.html

- 22. Samir Palnitkar, "Verilog HDL: A Guide to Digital Design and Synthesis," 2nd Edition, Prentice Hall, 2003

- 23.J Bhasker, "A Verilog HDL Primer", 3rd Edition, Star Galaxy Publishing, 2005.